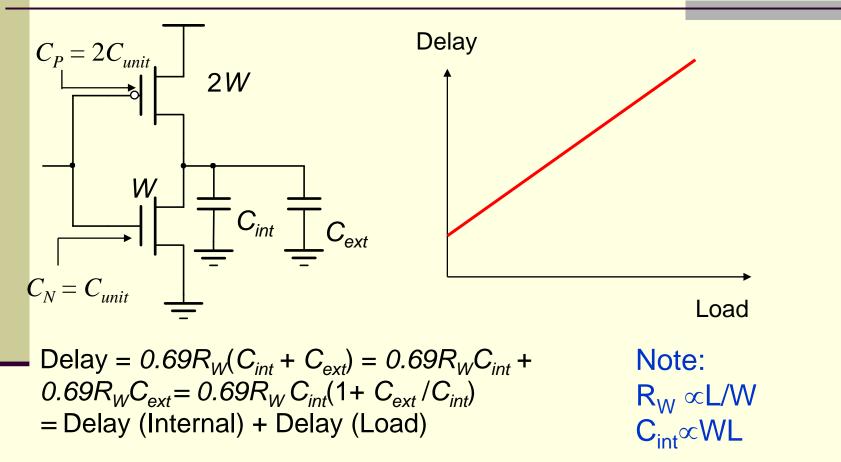

$C_{ext}$  – extrinsic load capacitance (fan-out + wiring)

Source: Rabaey

### Dynamic operation – 21

#### Inverter Delay

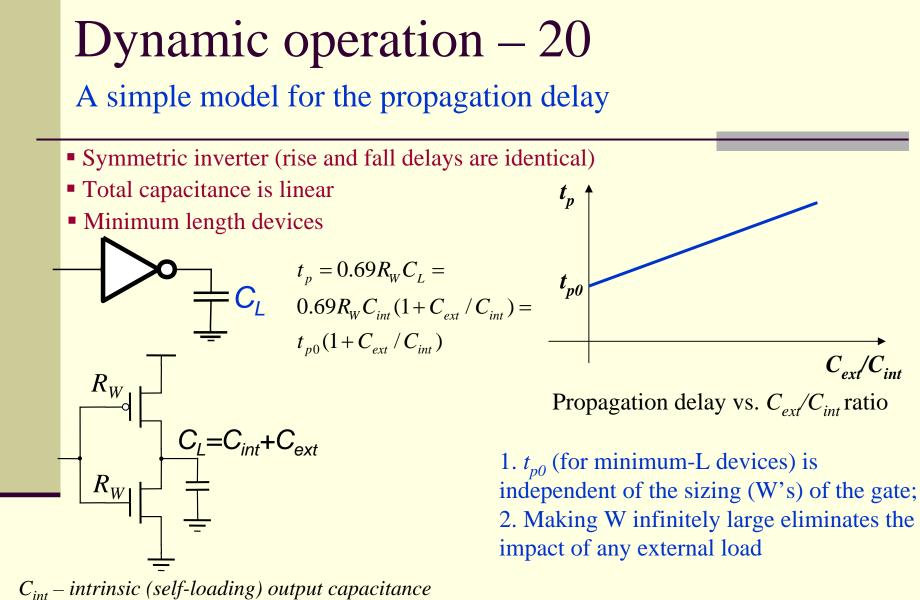

Minimum length devices

Assume that for W<sub>P</sub> = 2W<sub>N</sub>=2W

same pull-up and pull-down currents

approx. equal resistances R<sub>N</sub> = R<sub>P</sub>

approx. equal rise t<sub>pLH</sub> and fall t<sub>pHL</sub> delays

Analyze as an RC network

$$R_P = R_{unit} \left(\frac{W_P}{W_{unit}}\right)^{-1} \approx R_{unit} \left(\frac{W_N}{W_{unit}}\right)^{-1} = R_N = R_W$$

Delay (D):  $t_{pHL} = (\ln 2) R_N C_L$   $t_{pLH} = (\ln 2) R_P C_L$ Load for previous stage:  $C_{gin} = 3 \frac{W}{W_{unit}} C_{unit}$

## Dynamic operation – 22 Inverter Delay

### Dynamic operation – 23

#### Delay Formula

$$Delay \sim R_W(C_{int} + C_{ext})$$

$$t_{p} = kR_{W}C_{int}(1+C_{ext}/C_{int}) = t_{p0}(1+f/\gamma)$$

$C_{int} = \gamma C_{gin} \text{ with } \gamma \approx 1$   $f = C_{ext} / C_{gin} \text{ - effective fanout}$   $R = R_{unit} / W \text{ ; } C_{int} = W C_{unit}$  $t_{p0} = 0.69 R_{unit} C_{unit}$  Note:  $R_W \propto L/W$   $C_{int} \propto WL$   $t_{p0} \propto L^2 \rightarrow minimum L for$ minimum delay

Source: Rabaey

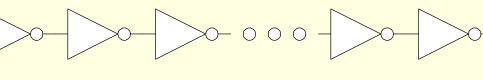

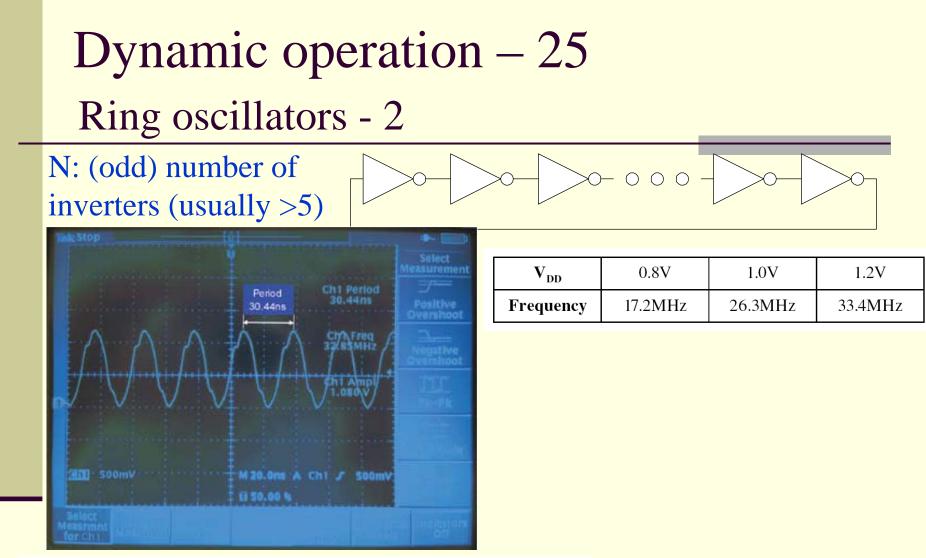

Dynamic operation – 24 Ring oscillators - 1

N: (odd) number of inverters (usually >5)

$$t_{p} = kR_{W}C_{int}(1+C_{ext}/C_{int}) = t_{p0}(1+f/\gamma)$$

$$C_{int} = \gamma C_{gin} \text{ with } \gamma \approx 1 \qquad f_{osc} = \frac{1}{2Nt_p} \rightarrow t_p = \frac{1}{2Nf_{osc}}$$

$$f = C_{ext}/C_{gin} = 1$$

Ring oscillators are used as process monitors to verify if a chip is faster or slower than nominally expected. Ex: 31-stage ring oscillator in a 180 nm process oscillates at 540 MHz.

Sources: Rabaey

Weste

Ring oscillator output as viewed with an oscilloscope. The time base is set to 20ns per division and the voltage scale is set to 500mV per division. The measured wave period is 30.44ns and the measured amplitude is 1.08V when the supply voltage is 1.2V.

Source: *www.keithley.com.cn/data?asset=51070*

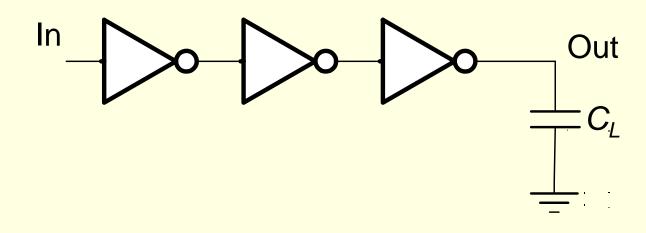

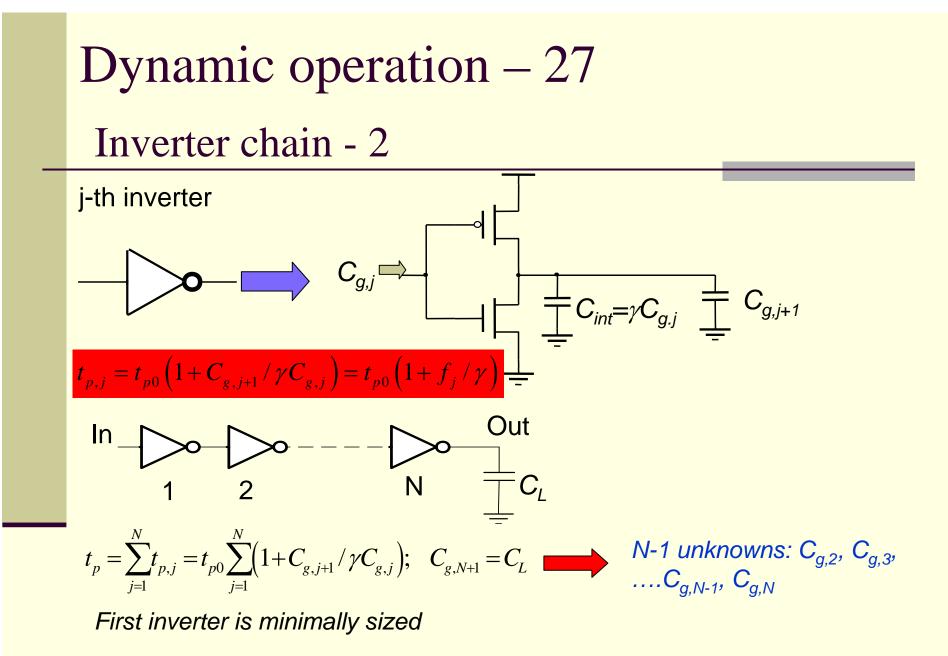

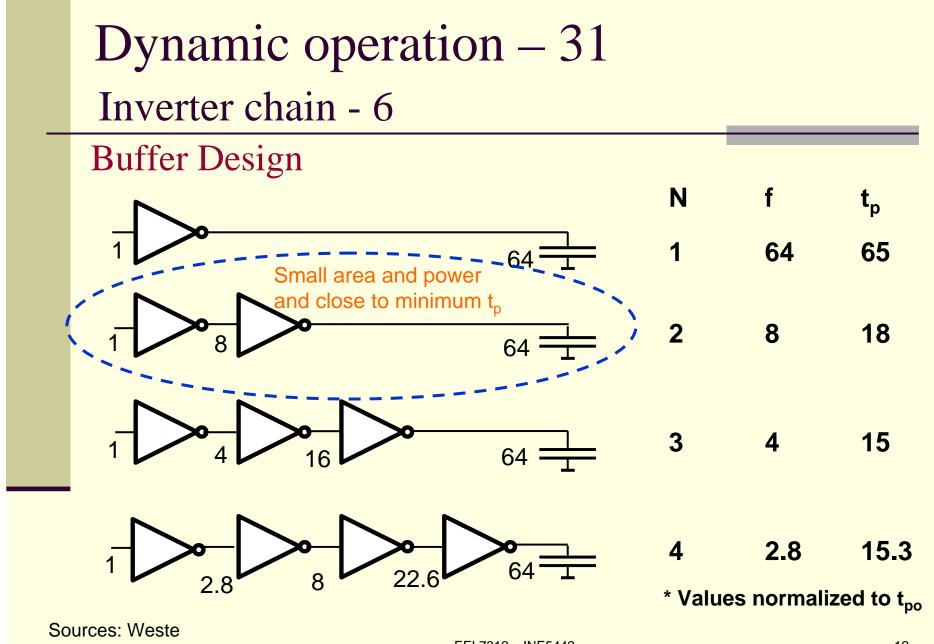

Dynamic operation – 26 Inverter chain - 1

If  $C_L$  is given:

- How many stages are needed to minimize the delay?

- How to size the inverters?

May need some additional constraints.

Source: Rabaey

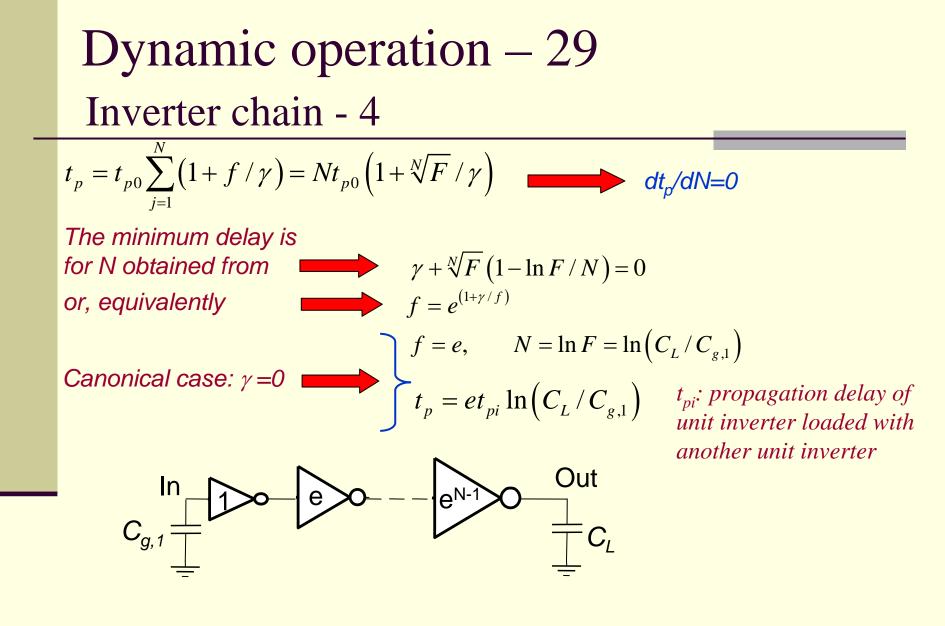

Dynamic operation – 28 Inverter chain - 3

Let's minimize  $t_p = \sum_{j=1}^{N} t_{p,j} = t_{p0} \sum_{j=1}^{N} (1 + C_{g,j+1} / \gamma C_{g,j}); \quad C_{g,N+1} = C_L$

Taking the N-1 derivatives partial derivatives  $C_{g,j} = \sqrt{C_{g,j-1}C_{g,j+1}}$ and equating them to 0 we find that

Thus, each inverter is sized up by the same factor f wrt the preceding gate

$$f = C_{g,j+1} / C_{g,j} = \sqrt[N]{C_L / C_{g,1}} = \sqrt[N]{F}$$

The minimum delay is

$$t_p = t_{p0} \sum_{j=1}^{N} (1 + f / \gamma) = Nt_{p0} (1 + \sqrt[N]{F} / \gamma)$$

What's N that minimizes delay?

Source: Rabaey

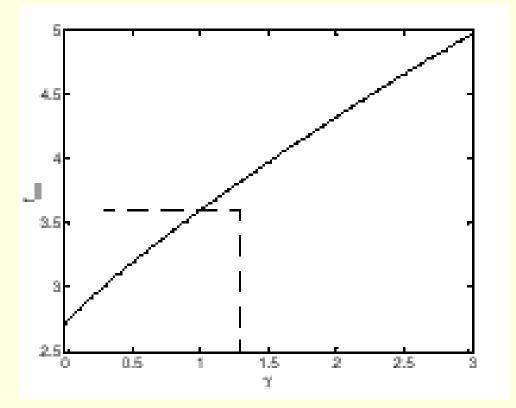

Dynamic operation – 30 Inverter chain - 5

Optimum effective fan-out  $f = \exp(1 + \gamma/f)$

Source: Rabaey

and Rabaey

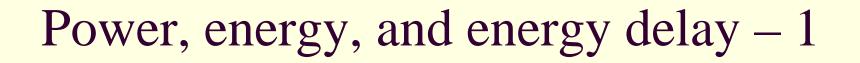

- Power is drawn from a voltage source attached to the V<sub>DD</sub> pin(s) of a chip.

- Instantaneous Power: Delivered by the power source

p(t) = i(t)v(t) $p(t) = i_{DD}(t)V_{DD}$

Average Power:

Energy:

$$E = \int_{0}^{T} p(t)dt = \int_{0}^{T} i(t)v(t)dt$$

$$P_{\text{avg}} = \frac{E}{T} = \frac{1}{T}\int_{0}^{T} i(t)v(t)dt$$

Source: Weste

Where Does Power Go in CMOS?

#### • Dynamic Power Consumption

**Charging and Discharging Capacitors**

#### Short Circuit Currents

Short Circuit Path between Supply Rails during Switching

#### • Leakage

Leaking diodes and transistors

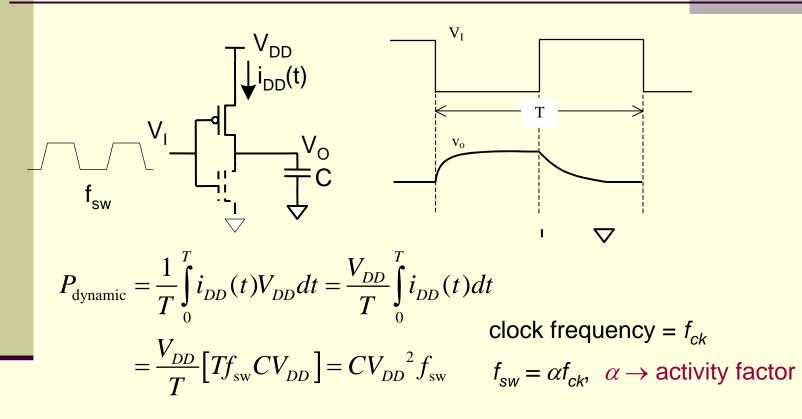

#### **Dynamic Power Dissipation**

#### **Dynamic Power Dissipation**

Where's the energy delivered by V<sub>DD</sub>?

One half of the energy is stored in C whereas the other half is converted into heat in the pull-up network

>  $E(M_N) = CV_{DD}^2/2$

$$E\left(M_{p}\right) = CV_{DD}^{2}/2$$

During the  $1 \rightarrow 0$  transition of the output, the energy stored on C is dissipated into the n-channel transistor

#### **Dynamic Power Dissipation**

#### For low power reduce C, $V_{DD}$ , and $f_{sw}$

Source: Weste

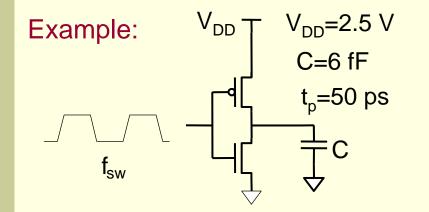

#### **Dynamic Power Dissipation**

Energy delivered by the power supply ( $E_{DD}$ ) to charge C  $E_{DD} = CV_{DD}^{2} = 6 \cdot 2.5^{2} = 37.5$  fJ Assume that  $f_{ck}=1/4t_{p}=5$  GHz For  $f_{sw}=f_{ck}=5$  GHz, the average dynamic power dissipation is

$$P_{\text{dynamic}} = CV_{DD}^{2} f_{\text{sw}} = 37.5 \cdot 5 \text{ fJ} \cdot \text{GHz} = 187.5 \ \mu\text{W}$$

For an activity factor of 0.1, the average dynamic power dissipation is ~ 18  $\mu$ W

One million identical inverters with the same activity factor of 0.1 would give a total power dissipation of ~ 18 W

Source: Weste

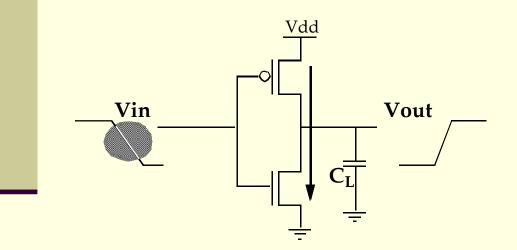

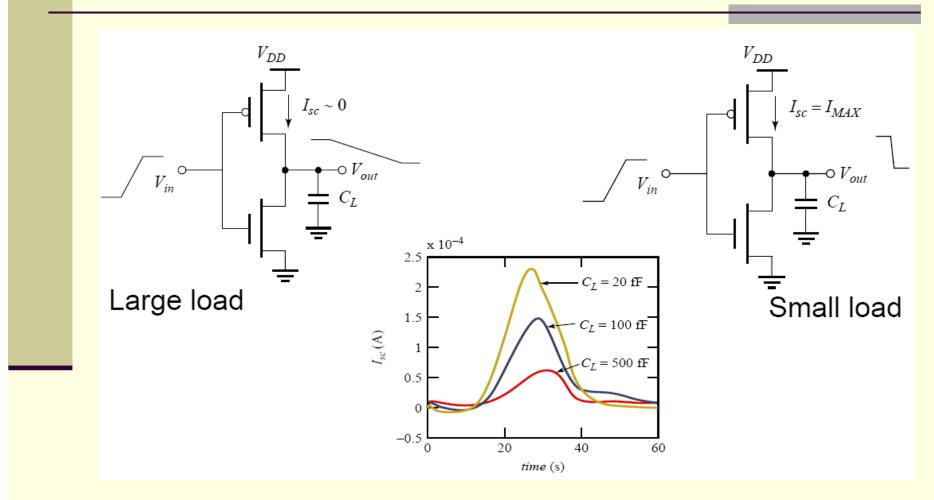

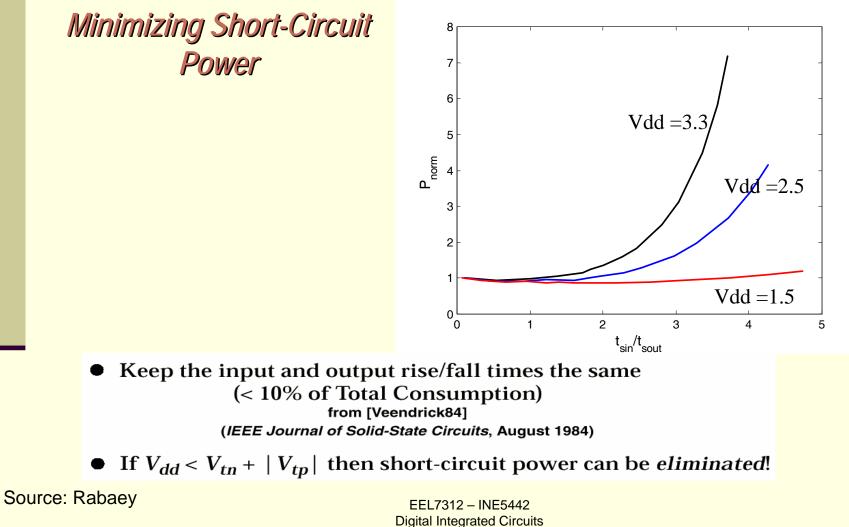

#### **Short Circuit Currents**

- When transistors switch, both nMOS and pMOS transistors may be momentarily ON at once

- Typically < 10% of dynamic power if rise/fall times are comparable for input and output

#### **Short Circuit Currents**

#### **Short Circuit Currents**

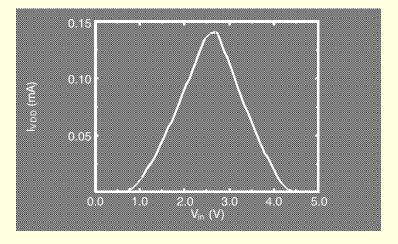

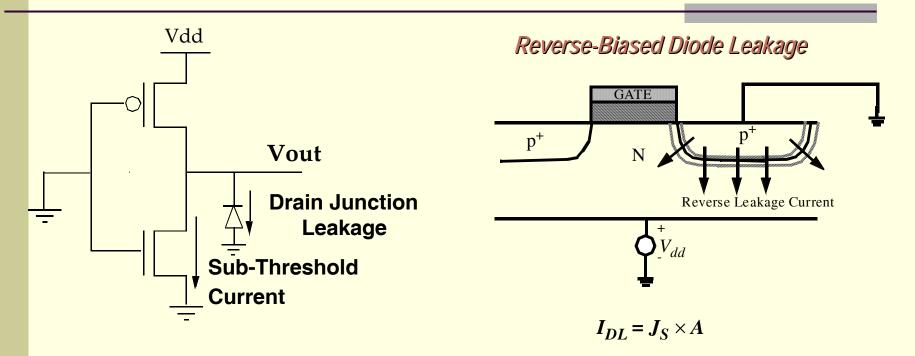

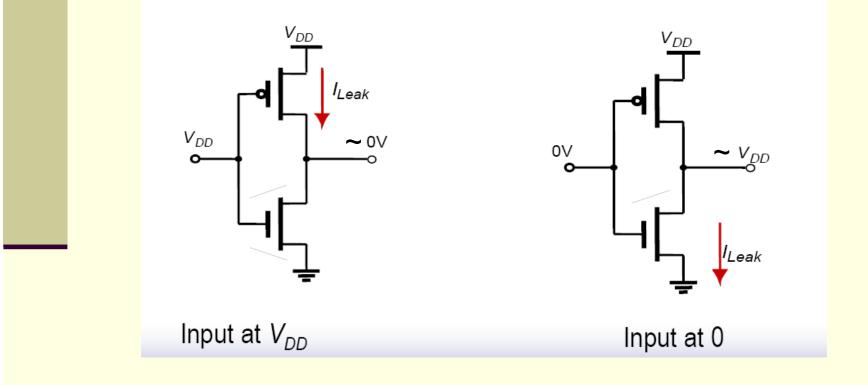

#### Leakage $\rightarrow$ static dissipation

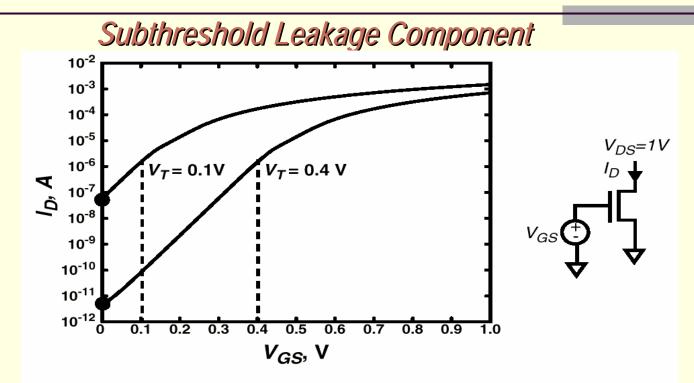

Sub-threshold current one of most compelling issues in low-energy circuit design!

#### $\textbf{Leakage} \rightarrow \textbf{static dissipation}$

Transistors that are supposed to be off - leak

#### Leakage $\rightarrow$ static dissipation

Leakage control is critical for low-voltage operation

In our simplified model, currents for  $V_{GS}$  below  $V_T$  were assumed to be zero. However, subthreshold current is very important, especially for advanced technologies (low  $V_T$ 's) and can be the major component of power dissipation.

Source: Rabaey

### Power, energy, and energy delay -13Leakage $\rightarrow$ static dissipation

Static power is due to the current that flows between supply rails in the absence of switching activity  $P_{\text{stat}} = I_{stat}V_{DD}$  $P_{\text{tot}} = P_{stat} + P_{dyn}$ Diode leakage + Charge/discharge Cs + subthreshold current short-circuit current P<sub>tot</sub> P<sub>stat</sub> 0 f<sub>sw</sub>

Source: Rabaey

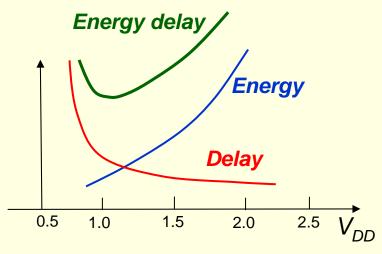

Power-Delay Product (PDP) = Average energy consumedper switching event  $(0 \rightarrow 1 \text{ or } 1 \rightarrow 0)$  $PDP = \frac{CV_{DD}^2}{PDP}$

Energy-Delay Product (EDP) = quality metric of gate =  $E \times t_p$

$$EDP = PDP \cdot t_p = \frac{CV_{DD}^2}{2}t_p$$