#### Universidade Federal de Santa Catarina

#### Centro Tecnológico

Departamento de Informática e Estatística Curso de Graduação em Ciências da Computação

## Sistemas Digitais

**INE 5406**

#### Aula 2-T

1. Projeto de ULA. Circuitos Digitais e Níveis de Abstração. Funcionamento e características temporais de registradores. Cadenciamento com sinal de relógio (clock) e análise de *timing*.

Prof. José Luís Güntzel guntzel@inf.ufsc.br

www.inf.ufsc.br/~guntzel/ine5406/ine5406.html

## O Mercado de Eletrônica de Consumo Dominância do Segmento *Personal Mobile Devices* (PMDs)

#### Computação de Propósito Geral

#### Computação de Propósito Específico

- Portabilidade (tamanho e peso)

- Alta capacidade de processamento (=alto desempenho)

- Baixíssimo consumo de energia

O Mercado de Eletrônica de Consumo Dominância do Segmento Personal Mobile Devices (PMDs)

Usam MPSoCs (*Multi-Processor Systems-on-a-Chip*), fornecidos por, ou licenciados de terceiros

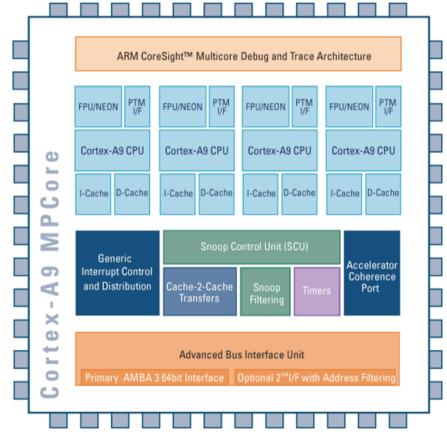

O Mercado de Eletrônica de Consumo

**Exemplo de MPSoC: ARM Cortex™ A9**

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0407f/index.html

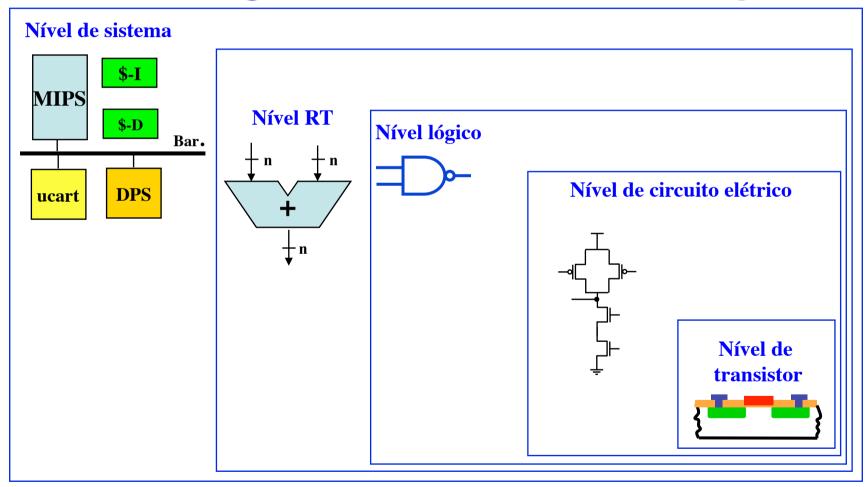

### Circuitos Digitais e Níveis de Abstração

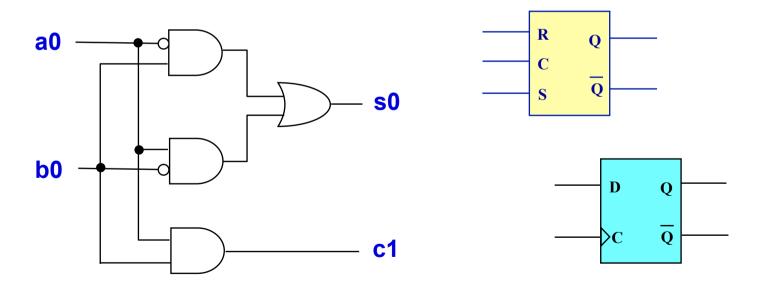

# Circuitos Digitais e Níveis de Abstração Nível Lógico:

- Circuitos vistos como associações de portas lógicas, latches e flip-flops (conforme visto em EEL5105).

- · Variáveis binárias de um bit cada.

# Circuitos Digitais e Níveis de Abstração Nível RT (Register Transfer):

Circuitos vistos como associações de componentes, feitos de portas lógicas (objeto desta disciplina).

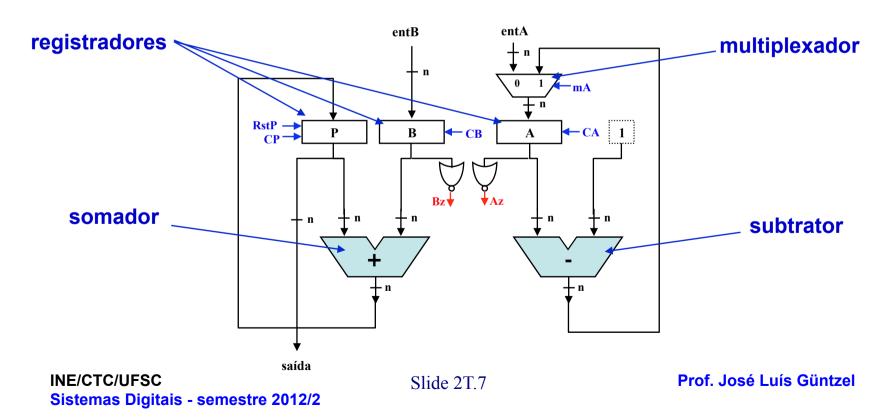

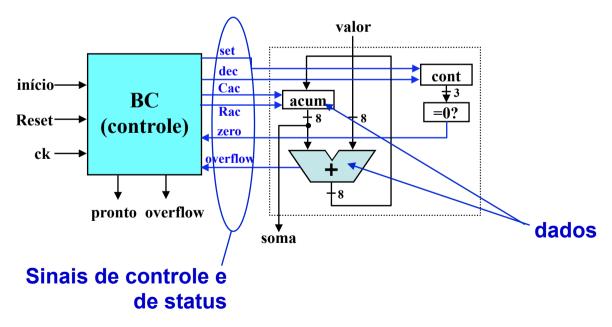

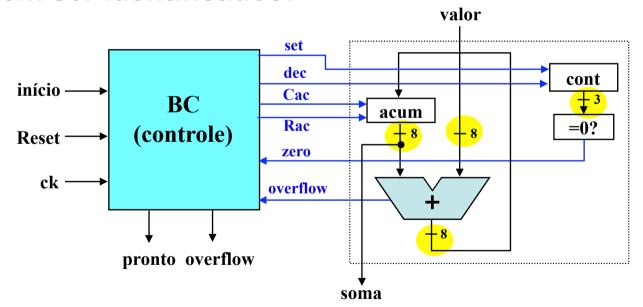

- Circuitos Digitais e Níveis de Abstração Nível RT (Register Transfer):

- Operações lógicas e aritméticas sobre vetores de bits, os quais representam números.

- Sinais de controle e de status.

Slide 2T.8

### Circuitos Digitais e Níveis de Abstração

| Matéria            | Nível de abstração        | Componentes                                                                                                                                                                                                              |  |

|--------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Circuitos Digitais | Lógico                    | <ul><li>Portas lógicas</li><li>Latches</li><li>Flip-flops</li></ul>                                                                                                                                                      |  |

| Sistemas Digitais  | RT<br>(register-transfer) | <ul> <li>Somadores</li> <li>Subtratores</li> <li>ULAs (= unidades funcionais compostas)</li> <li>Registradores</li> <li>Memórias</li> <li>Multiplexadores</li> <li>Decodificadores</li> <li>Bloco de controle</li> </ul> |  |

Representando Dados em Circuitos Digitais Exemplo: um circuito mais complexo.

Fios que representam variáveis de mais de um bit devem ser identificados!

### Tipos de Circuitos Digitais

#### 1. Circuitos Combinacionais:

Não são capazes de reter os sinais (dados) gerados em suas saídas (tampouco os sinais que são aplicados em suas de entradas). "As saídas dependem apenas das entradas."

#### Usados para construção de:

- •Circuitos aritméticos e lógicos (somadores, subtratores, deslocadores, ULAs, comparadores, multiplexadores, decodificadores ...)

- •Lógica de próximo estado e lógica de saída, nos circuitos de controle

### Tipos de Circuitos Digitais

#### 2. Circuitos Sequenciais:

São capazes de armazenar os sinais de entrada (enquanto estiverem alimentados com energia). "As saídas dependem das entradas e do estado que está armazenado."

#### Usados para construção de:

• Registradores (latches e flip-flops)

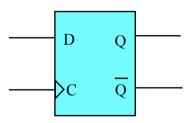

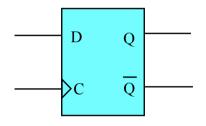

## Flip-flop D Disparado Pela Borda Ascendente (ou sensível à borda ascendente ou à borda de subida...)

símbolo

tabela de transição de estados

| C          | D | $Q_{t+1}$ |

|------------|---|-----------|

| <b>≠</b> ↑ | X | $Q_t$     |

| 1          | 0 | 0         |

| 1          | 1 | 1         |

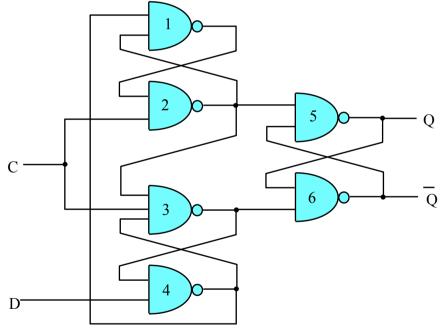

#### circuito com portas nand

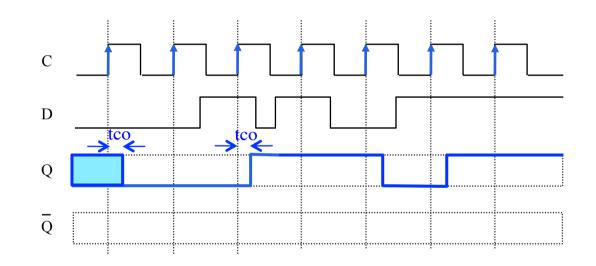

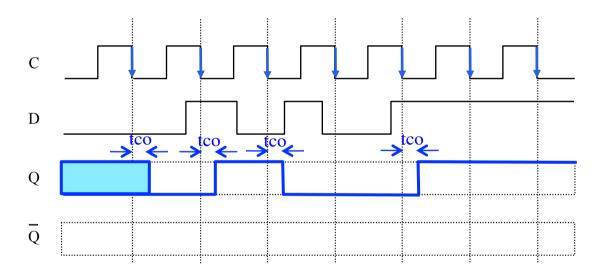

## Flip-flop D Disparado Pela Borda Ascendente Exemplo de funcionamento

tabela de transição de estados

| C          | D | $Q_{t+1}$ |

|------------|---|-----------|

| <b>≠</b> ↑ | X | $Q_{t}$   |

| 1          | 0 | 0         |

| 1          | 1 | 1         |

Obs: Nesta disciplina assumiremos que o atraso da saída Q' é idêntico ao atraso da saída Q. Assim, a saída Q' será o "espelho" da saída Q.

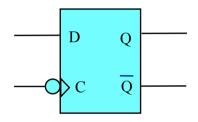

## Flip-flop D Disparado Pela Borda Descendente Exemplo de funcionamento

tabela de transição de estados

| С            | D | $Q_{t+1}$ |

|--------------|---|-----------|

| ≠↓           | X | $Q_{t}$   |

| $\downarrow$ | 0 | 0         |

| $\downarrow$ | 1 | 1         |

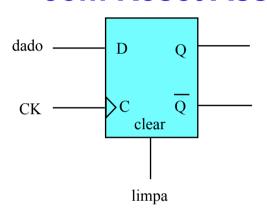

Flip-flop D Disparado Pela Borda Ascendente, com Reset Assíncrono

Exemplo de funcionamento

tabela de transição de estados

| clear | C          | D | $Q_{t+1}$      |

|-------|------------|---|----------------|

| 0     | <b>≠</b> ↑ | X | Q <sub>t</sub> |

| 0     | 1          | 0 | 0              |

| 0     | 1          | 1 | 1              |

| 1     | X          | X | 0              |

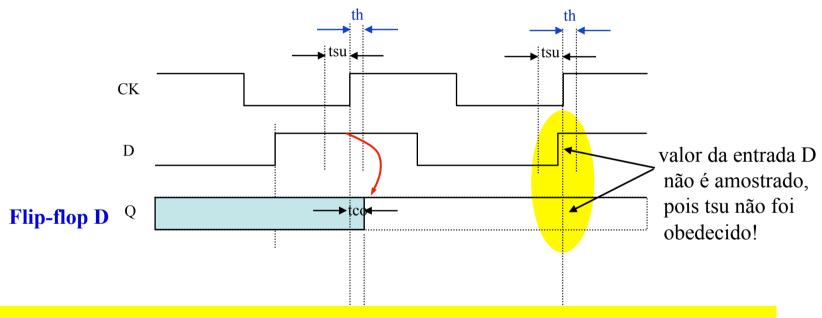

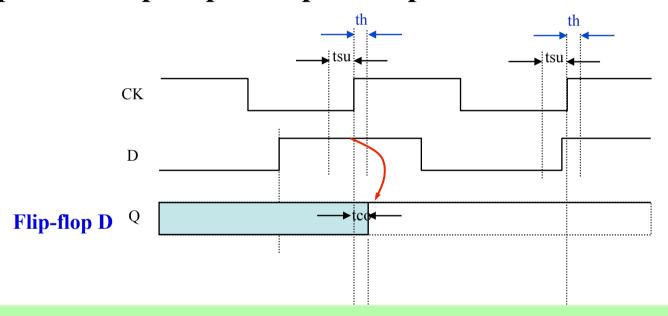

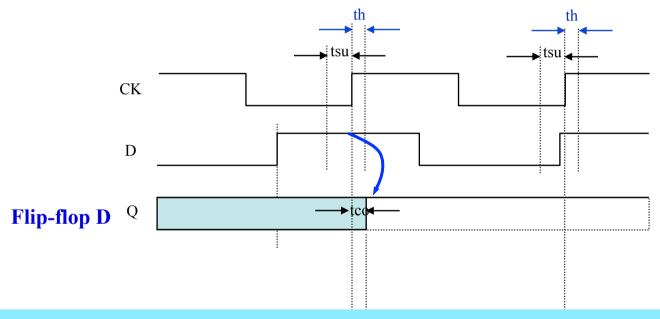

#### Características Temporais de Flip-flops

Supor um Flip-flop D disparado pela Borda de Subida

#### tsu = Tempo de Preparação (setup time)

"Tempo antes da borda ativa de ck (subida, neste caso) durante o qual a entrada D já deve estar em seu valor estável."

#### Características Temporais de Flip-flops

Supor um Flip-flop D disparado pela Borda de Subida

#### th = Tempo de Manutenção (hold time)

"Tempo, a partir da borda ativa de ck (subida, neste caso), durante o qual a entrada D deve permanecer estável."

#### Características Temporais de Flip-flops

Supor um Flip-flop D disparado pela Borda de Subida

tco (ou td) = Time from clock to output (ou Tempo ou Atraso de Carga)

"Atraso, em relação à borda ativa de ck (subida, neste caso), para o valor amostrado a partir da entrada D aparecer nas saídas Q e Q."

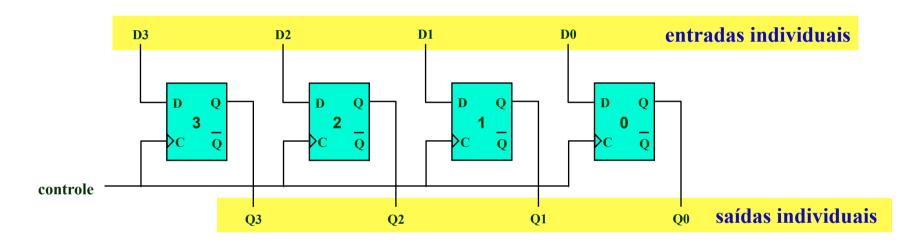

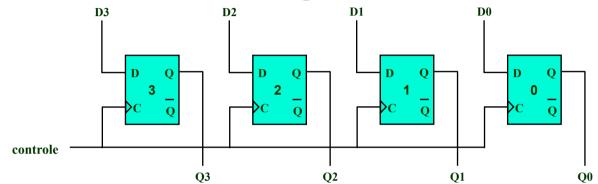

#### Registrador com Carga Paralela

- Existe um FF para cada bit a ser armazenado

- Todos os FFs "obedecem" a um mesmo sinal de controle

- O termo "carga paralela" refere-se ao fato de existir uma entrada para cada bit, de modo que é possível carregar simultaneamente todos os bits do dado

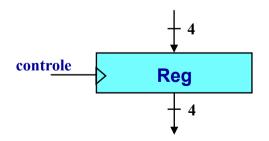

#### Símbolo no nível RT

Prof. José Luís Güntzel

#### Registrador com Carga Paralela

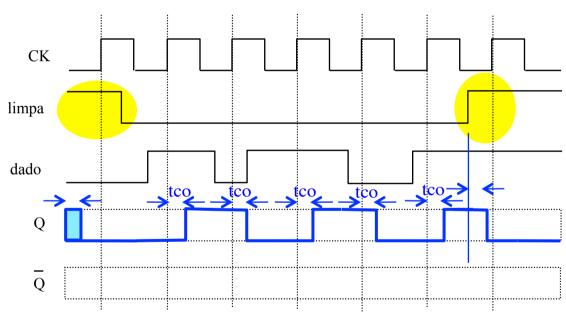

#### Exemplo de funcionamento (assumindo que tsu, th e td são satisfeitos)

A cada borda de subida de "controle" um novo dado é amostrado e fica armazenado no registrador (até a próxima borda de subida de "controle")

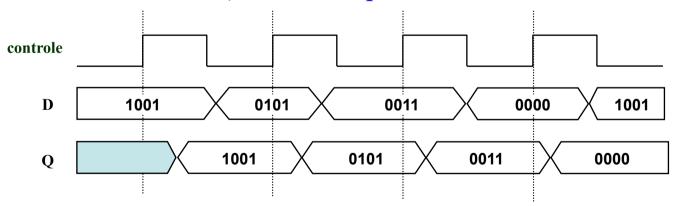

#### Registrador com Carga Paralela

- Peculiaridade: a cada borda de subida de "controle" um novo dado é amostrado, mesmo que não se queira amostrar um dado novo...

- Porém, às vezes pode ser necessário que o registrador obedeça a um sinal de controle sincronizado com o sinal de relógio. (Solução na próxima transparência...)

### Cadenciamento de Sistemas Digitais

- A maior parte dos sistemas digitais são sincronizados por um sinal monótono denominado relógio (ou *clock*, em inglês).

- Sistemas digitais cadenciados por sinal de relógio são denominados síncronos.

- No projeto de sistemas digitais síncronos, registradores são utilizados.

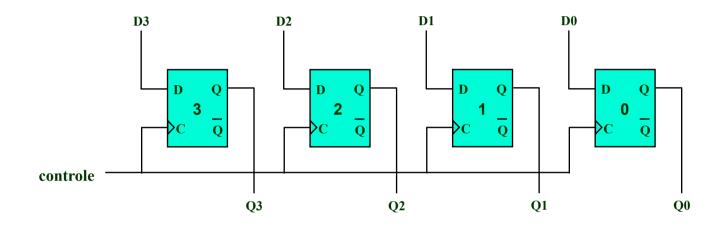

#### Sinal de Relógio (ou Clock)

#### **Nomenclatura**

borda ascendente = borda de subida = borda positiva = flanco de subida etc

borda descendente = borda de descida = borda negativa = flanco de descida etc

#### Características:

- **Período** (T): tempo entre duas bordas consecutivas de mesmo tipo. Medido em submúltiplos do segundo (ms, μs, ns)

- Frequência: f = 1/T, medida em múltiplos do hertz (kHz, MHz, GHz)

- *Duty cycle*: T1/T x 100 %, onde T1 é o tempo entre uma borda ascendente e a borda descendente que a segue.

## Estimativa do Período do Relógio

Exemplo 1: Estime o período do relógio para um circuito combinacional cujo atraso crítico é 10 ns.

#### **Preliminares:**

```

1 ns (1 nanossegundo) = 1 x 10<sup>-9</sup> s

T = 1/f \Rightarrow f = 1/T

1/1s = 1 Hz

```

#### Cálculo:

```

f = 1/(10 \times 10^{-9}) Hz = 0.1 \times 10^{+9} Hz = 100 \times 10^{+6} Hz = 100 MHz

```

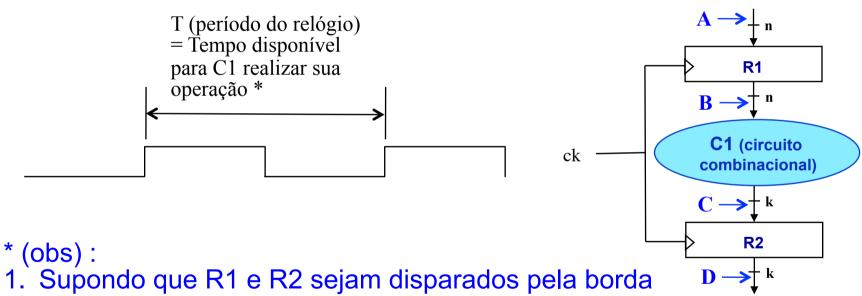

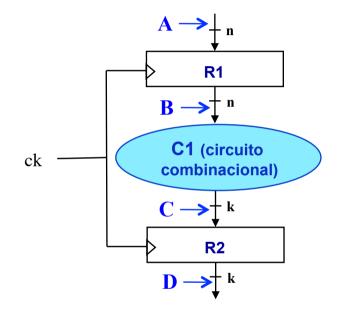

## Cadenciamento de Sistemas Digitais

Registradores são usados para criar "barreiras temporais" que isolam os circuitos combinacionais

de subida de ck.

2. Aproximação grotesca; falta considerar as

Aproximação grotesca; falta considerar as características temporais dos registradores R1 e R2.

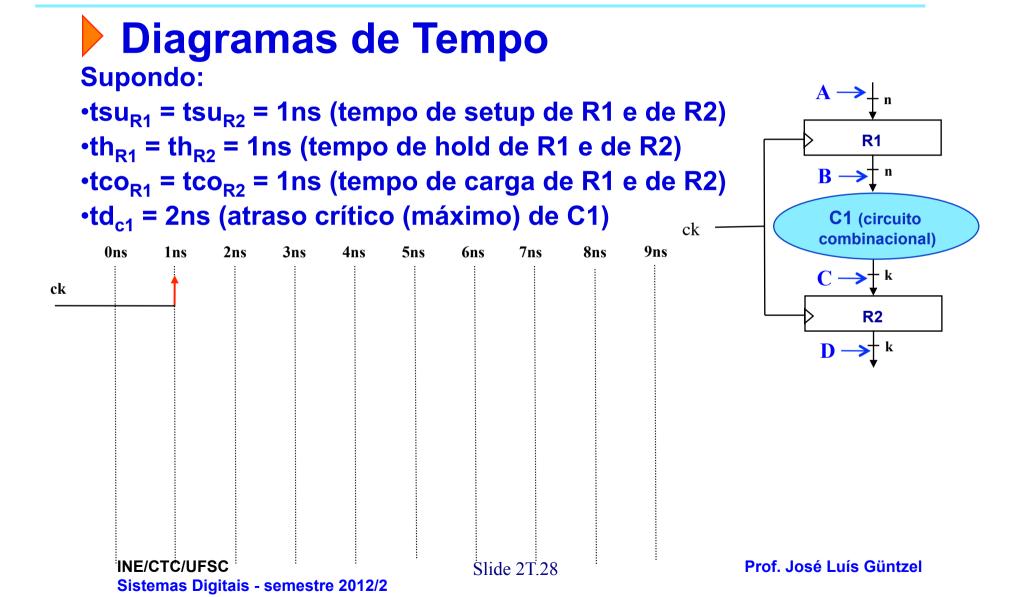

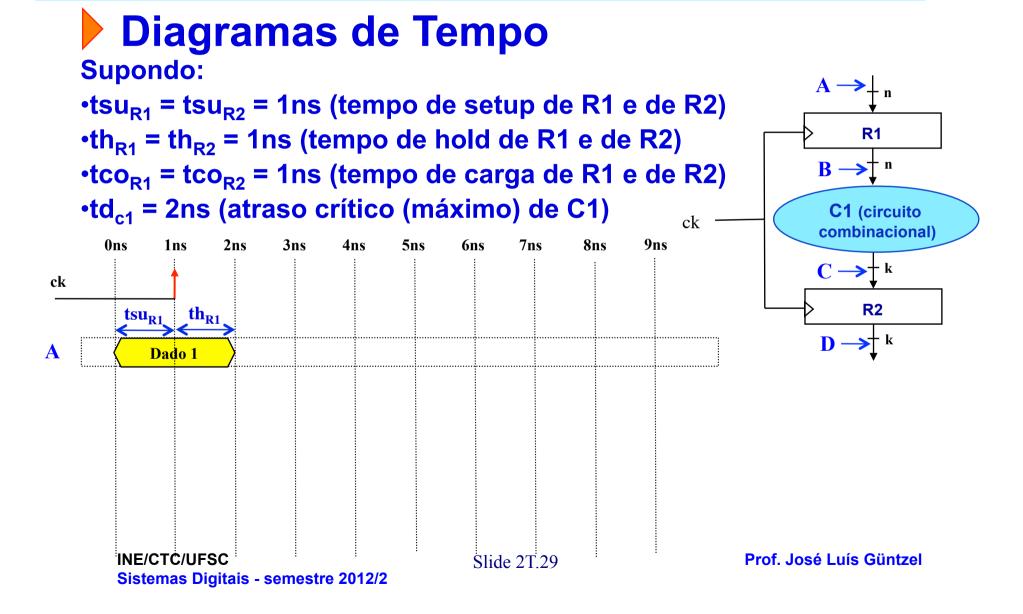

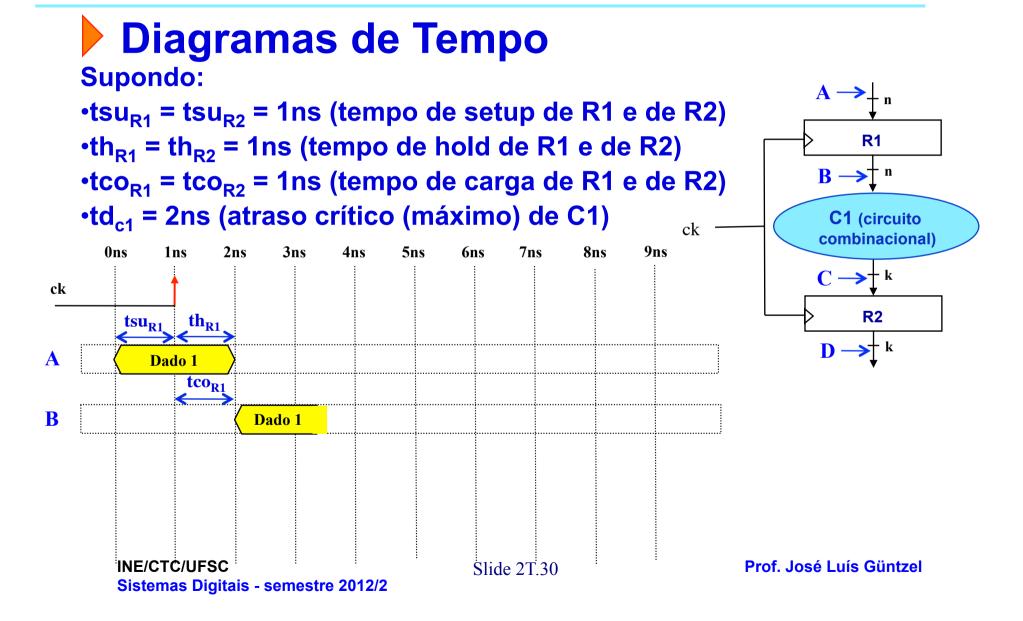

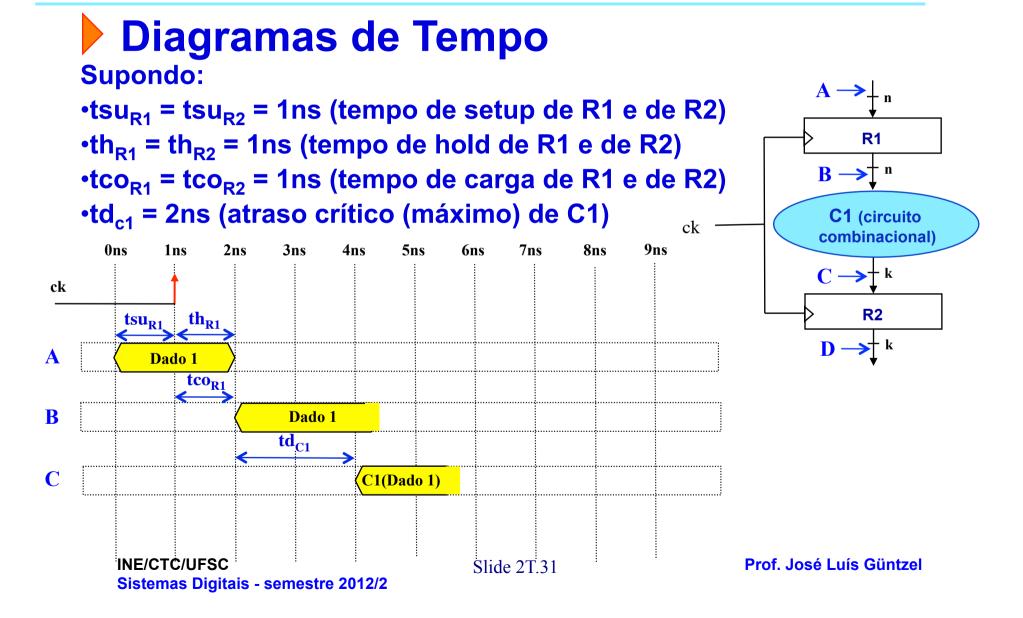

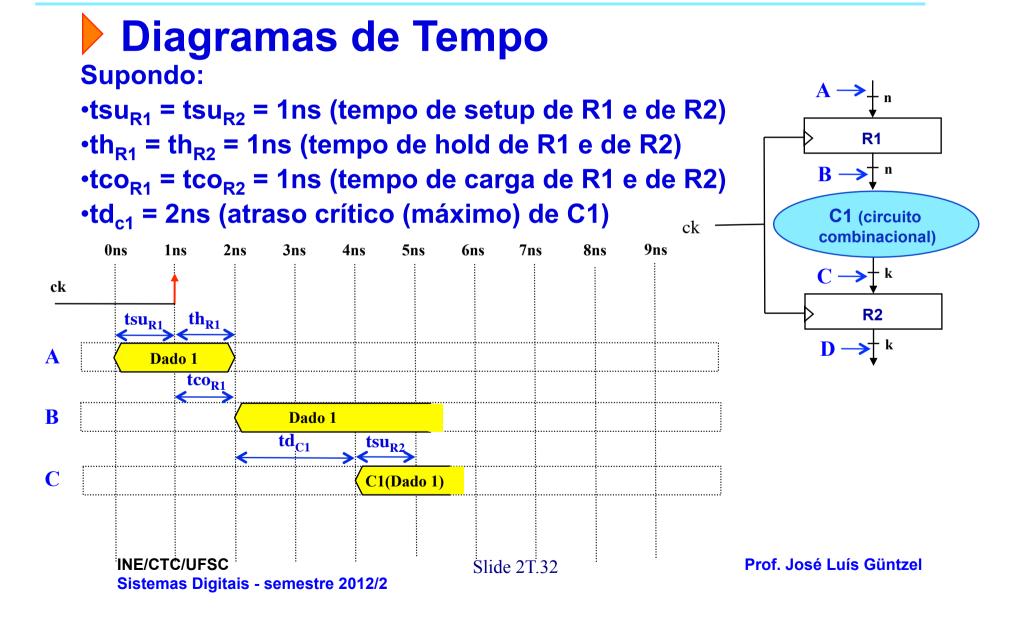

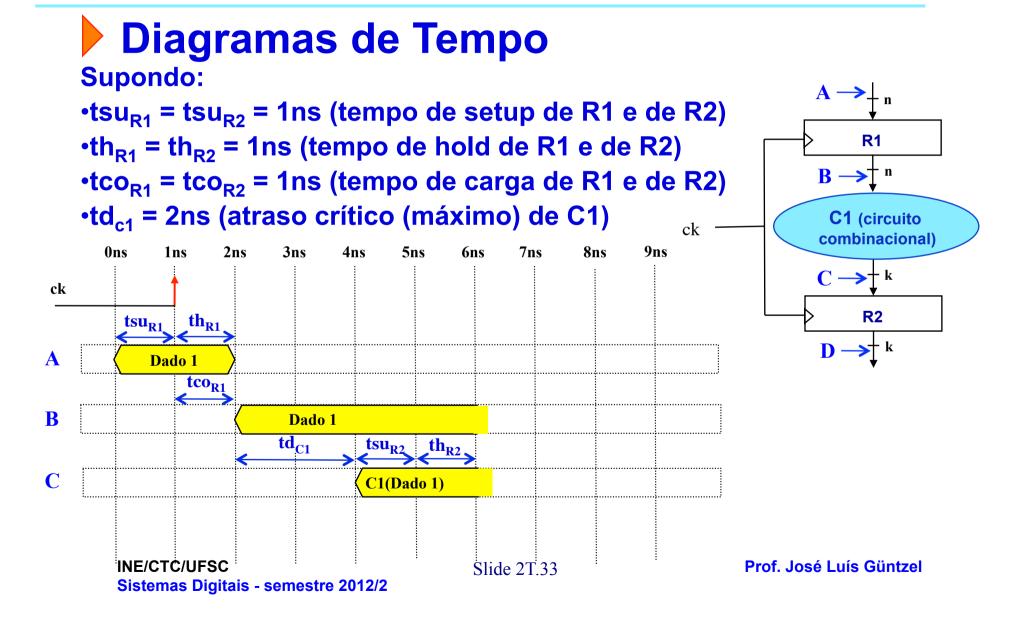

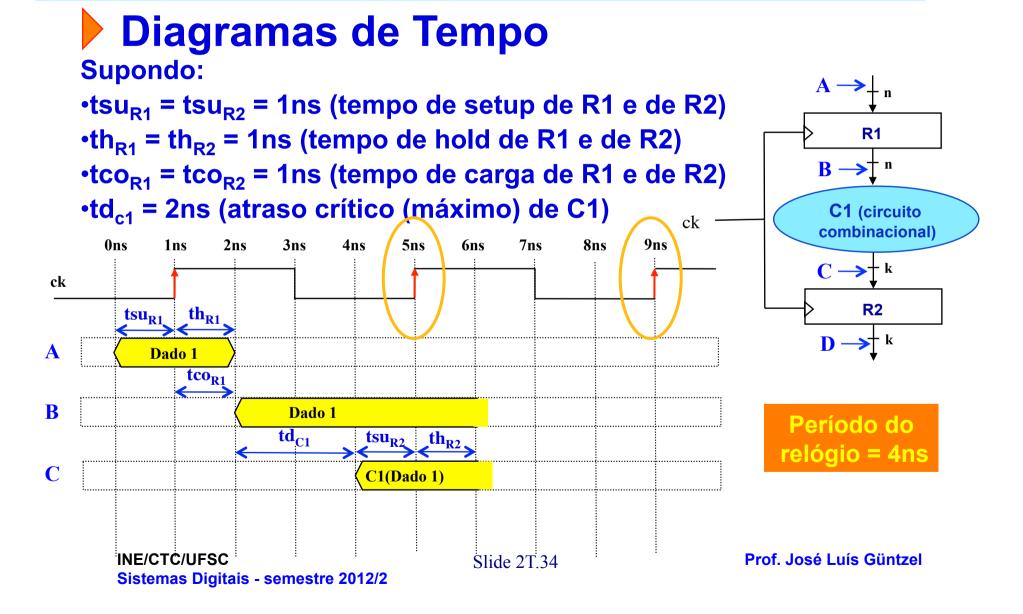

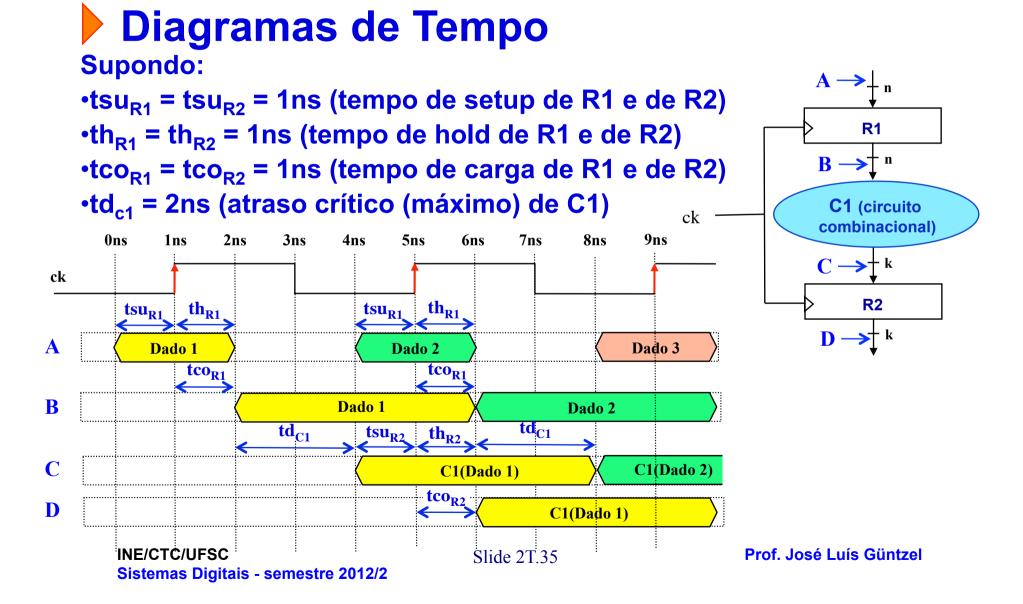

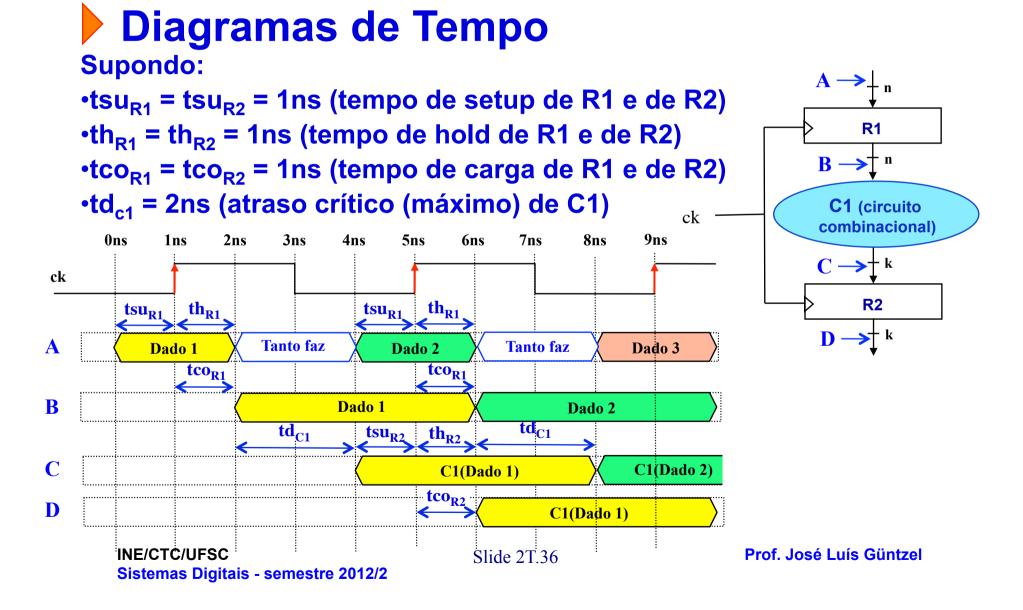

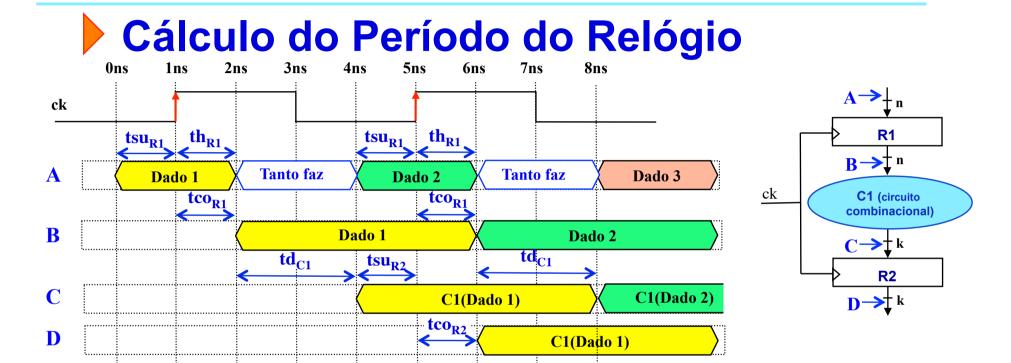

#### Diagramas de Tempo

#### **Supondo:**

```

•tsu<sub>R1</sub> = tsu<sub>R2</sub> = 1ns (tempo de setup de R1 e de R2)

•th<sub>R1</sub> = th<sub>R2</sub> = 1ns (tempo de hold de R1 e de R2)

•tco<sub>R1</sub> = tco<sub>R2</sub> = 1ns (tempo de carga de R1 e de R2)

•td<sub>c1</sub> = 2ns (atraso crítico (máximo) de C1)

```

Conclusão. O período do relógio pode ser calculado por:

## Diagramas de Tempo

Pergunta: Como estimar td<sub>C1</sub>?

Notar que C1 é um circuito combinacional

Estimando o Atraso Crítico de Circuito Combinacional

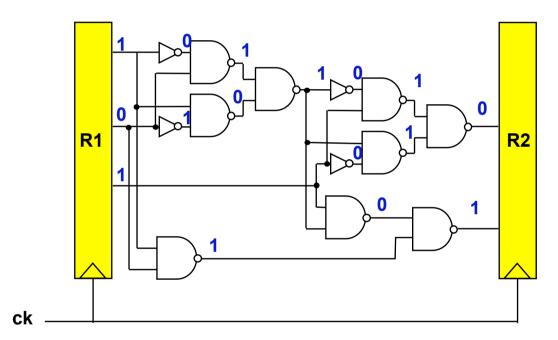

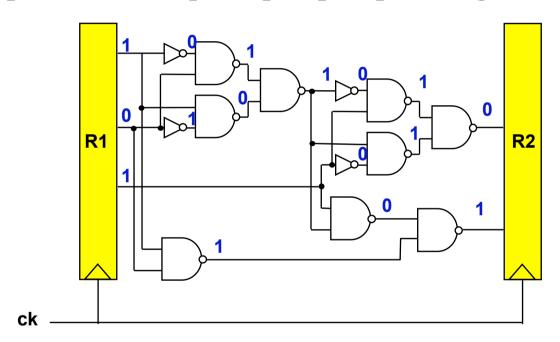

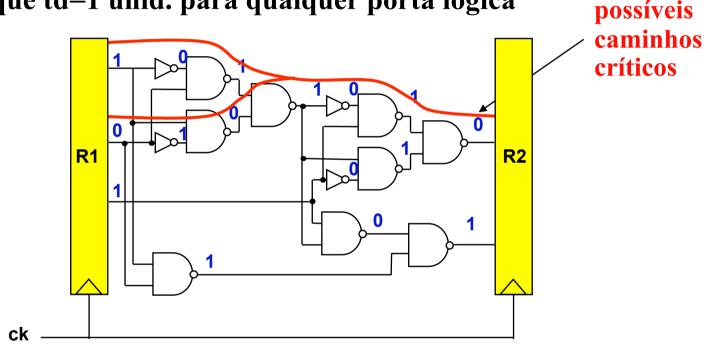

Supondo que td=1 unid. para qualquer porta lógica

#### Estimando o Atraso Crítico de Circuito Combinacional

Supondo que td=1 unid. para qualquer porta lógica

#### Possíveis Técnicas:

1. Simulação: repetir a análise para cada um dos 2<sup>n</sup> vetores de entrada.

Estimando o Atraso Crítico de Circuito Combinacional

Supondo que td=1 unid. para qualquer porta lógica

#### Possíveis Técnicas:

- 1. Simulação: repetir a análise para cada um dos 2<sup>n</sup> vetores de entrada.

- 2. Análise de Timing (STA): analisar os atrasos dos caminhos entre R1 e R2.